# TTL MEMORIES

# SERIES 54/74, 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

BULLETIN NO. DL-S 7512258, MAY 1975

- Titanium-Tungsten (Ti-W) Fuse Links for Fast, Low-Voltage, Reliable Programming

- Full Decoding and Chip Select Simplify System Design

- All Schottky-Clamped PROM's Offer: Fast Chip Select to Simplify System Decode Choice of Three-State or Open-Collector Outputs P-N-P Inputs for Reduced Loading on System Buffers/Drivers

- Applications Include: Microprogramming/Firmware Loaders Code Converters/Character Generators Translators/Emulators Address Mapping/Look-Up Tables

| TYPE NUMBER    | R (PACKAGES)                    | BIT SIZE                 | ουτρυτ         | TYPICAL ACC     | ESS TIME (ns)       |

|----------------|---------------------------------|--------------------------|----------------|-----------------|---------------------|

| –55°C to 125°C | $0^{\circ}$ C to $70^{\circ}$ C | (ORGANIZATION)           | CONFIGURATION  | FROM<br>ADDRESS | FROM<br>CHIP SELECT |

| SN54186(J, W)  | SN74186(J, N)                   | 512 bits<br>(64 W x 8 B) | open-collector | 50              | 55                  |

| SN54188A(J, W) | SN74188A(J,N)                   | 050 1.14                 | open-collector | 30              | 34                  |

| SN54S188(J, W) | SN74S188(J, N)                  | 256 bits<br>(32 W x 8 B) | open-collector | 25              | 12                  |

| SN54S288(J, W) | SN74S288(J, N)                  | (32 W X 6 B)             | three-state    | 25              | 12                  |

| SN54S287(J, W) | SN74S287(J, N)                  | 1024 bits                | three-state    | 42              | 15                  |

| SN54S387(J, W) | SN74S387(J, N)                  | (256 W × 4 B)            | open-collector | 42              | 15                  |

| SN54S470(J)    | SN74S470(J, N)                  | 2048 bits                | open-collector | 50              | 20                  |

| SN54S471(J)    | SN74S471(J, N)                  | (256 W x 8 B)            | three-state    | 50              | 20                  |

| SN54S472(J)    | SN74S472(J, N)                  | 4096 bits                | three-state    | 55              | 20                  |

| SN54S473(J)    | SN74S473(J, N)                  | (512 W x 8 B)            | open-collector | 55              | 20                  |

| (64 W                                                                                                        | 512 BITS<br>ORDS BY 8 BITS<br>'186                                               | ) (32 WORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6 BITS<br>DS BY 8 BITS)<br>S188, 'S288   | (256 WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BITS<br>S BY 4 BITS)<br>, 'S387                                                                                                                                                                           | (256 WORD                                                                                                  | 3 BITS<br>IS BY 8 BITS)<br>), 'S471                                                                                                                                                                                                                            | 4096 1<br>(512 WORDS)<br>S472,                                                                             | BY 8 BITS)                                                                                          |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| NC 12<br>NC 22<br>ADA 32<br>ADB 42<br>CS1 62<br>CS2 72<br>ADD 82<br>ADE 92<br>ADE 102<br>GND 1 112<br>NC 122 | 223<br>221<br>221<br>220<br>219<br>219<br>219<br>219<br>219<br>219<br>219<br>219 | VCC 00 1 1<br>GND 2 00 2 2 C<br>00 1 00 3 3 C<br>00 2 00 4 4 C<br>00 3 00 5 5 C<br>00 4 00 6 6 C<br>00 5 00 7 7 C<br>00 6 GND 8 C<br>10 7<br>10 8<br>10 1<br>10 | 14 AD E<br>13 AD D<br>12 AD C<br>11 AD B | AD G 1<br>AD F 2<br>AD E 3<br>AD 4<br>AD 4<br>AD 4<br>AD 4<br>AD 5<br>AD 6<br>AD 7<br>AD 7 | )16         VCC           )15         AD H           )14         CS 2           )13         CS 1           )12         DO 1           )11         DO 2           )10         O3           )9         DO 4 | AD A 1C<br>AD B 2C<br>AD C 3C<br>AD D 4C<br>AD E 5C<br>DO 1 6C<br>DO 2 7C<br>DO 3 8C<br>DO 4 9C<br>GND 10C | >20         Vcc           >19         AD H           >18         AD G           >17         AD F           >16         CS 2           >15         CS 1           >14         D08           >13         D07           >12         D06           >11         D05 | AD A 10<br>AD B 20<br>AD C 30<br>AD C 40<br>AD E 50<br>DO 1 60<br>DO 2 70<br>DO 3 80<br>DO 4 90<br>GND 100 | 20 VCC<br>19 AD 1<br>18 AD H<br>17 AD 6<br>16 AD F<br>15 C5<br>14 D08<br>13 D07<br>12 D06<br>11 D05 |

Pin assignments for all of these memories are the same for all packages.

NC–No internal connection <sup>†</sup>TO is used for testing purposes The logic at TO is undefined.

### description

These monolithic TTL programmable read-only memories (PROM's) feature titanium-tungsten (Ti-W) fuse links with each link designed to program in one millisecond or less. The Schottky-clamped versions of these PROM's offer considerable flexibility for upgrading existing designs or improving new designs as they feature full Schottky clamping for improved performance, low-current MOS-compatible p-n-p inputs, choice of bus-driving three-state or open-collector outputs, and improved chip-select access times.

The high-complexity 2048- and 4096-bit PROM's can be used to significantly improve system density for fixed memories as all are offered in the 20-pin dual-in-line package having pin-row spacings of 0.300 inch.

# SERIES 54/74, 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

#### description (continued)

Data can be electronically programmed, as desired, at any bit location in accordance with the programming procedure specified. All PROM's, except the 'S287 and 'S387, are supplied with a low-logic-level output condition stored at each bit location. The programming procedure open-circuits Ti-W metal links, which reverses the stored logic level at selected locations. The procedure is irreversible; once altered, the output for that bit location is permanently programmed. Outputs never having been altered may later be programmed to supply the opposite output level. Operation of the unit within the recommended operating conditions will not alter the memory content.

A low level at the chip-select input(s) enables each PROM except the '186, which is enabled by a high level at both chip-select inputs. The opposite level at any chip-select input causes the outputs to be off.

The three-state output offers the convenience of an open-collector output with the speed of a totem-pole output; it can be bus-connected to other similar outputs yet it retains the fast rise time characteristic of the TTL totem-pole output. The open-collector output offers the capability of direct interface with a data line having a passive pull-up.

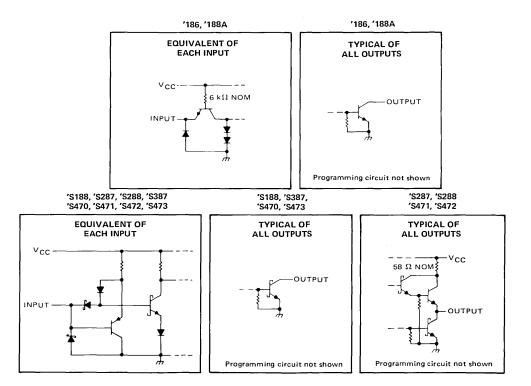

#### schematics of inputs and outputs

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage (see Note 1)           |                        | 7 V   |

|---------------------------------------|------------------------|-------|

| Input voltage                         |                        | 5.5 V |

|                                       |                        |       |

| Operating free-air temperature range: | SN54', SN54S' Circuits | 25°C  |

| · - · ·                               | SN74', SN74S' Circuits | 70°C  |

| Storage temperature range             |                        | 50°C  |

|                                       |                        |       |

NOTE 1: Voltage values are with respect to network ground terminal (GND 2 of '186),. For '186 GND 1 and both GND 2 terminals are all connected to system ground except during programming. The supply-voltage rating does not apply during programming of the '188, '188A, or the 54S/74S PROM's.

# TYPES SN54186, SN74186 PROGRAMMABLE READ-ONLY MEMORIES

### recommended conditions for programming

|                                            |            | MIN  | NOM                   | MAX    | UNI |

|--------------------------------------------|------------|------|-----------------------|--------|-----|

| Supply voltages (see Note 2)               | Vcc        | 4.75 | 5                     | 5.25   | v   |

| Supply voltages (see Note 2)               | GND 1      | -5   |                       | -6†    |     |

| Input conditions (see Note 3 and 4)        | High level |      | pen circu<br>equivale |        |     |

|                                            | Low level  | -5   |                       | -6†    | V   |

| Output voltage                             |            |      |                       | -6.5†‡ | V   |

| Output current, output being programmed    |            | 95   | -120                  | -130   | mA  |

| Duration of programming pulse (see Note 5) |            | 1    |                       | 20     | ms  |

| Programming duty cycle                     |            |      | 25                    | 35     | %   |

| Free-air temperature                       |            | 0    |                       | 55     | °c  |

<sup>†</sup>Absolute maximum ratings.

$^{\ddagger}$ Clamp to ensure output does not exceed -0.5 V with respect to GND 1.

- NOTES: 2. Voltage values are with respect to the GND 2 terminals

- 3. The high-level (off) output of a Series 54/74 or 54S/74S open-collector gate with no pull-up resistor meets the requirements for a high-level input condition.

- 4. The low-level input voltage must be within  $\pm 0.5$  volts of the applied voltage at GND 1.

- 5. Programming is guaranteed if the pulse is applied to the output for 10 ms. Typically, programming occurs in less than 1 ms.

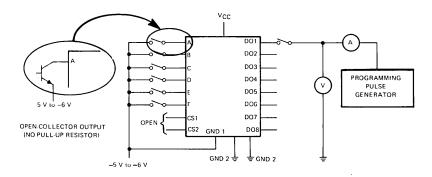

#### step-by-step programming procedure

Programming the SN54186 or SN74186 is performed individually for each of the 512 bit locations and consists basically of applying a current pulse to each output terminal where a low logic level is to be changed to a high (off) level. The power supply and ground connections described below are designed to ensure that alteration of the memory content occurs during the programming procedure only.

- 1. Connect the memory as shown in Figure 1. To address a particular word in the memory, set the input switches to the binary equivalent of that word where a low logic level is as specified under "recommended conditions for programming" and a high logic level is either an open circuit or connection to an open-collector TTL gate with no pull-up resistor.

- 2. Apply a programming current pulse as specified to the pin associated with the first bit to be changed from a low-level to a high-level output.

- Repeat Step 2 for each high-level output desired in the word addressed (program only one bit at a time). Any bit

that is to remain at a low level should have its respective output open-circuited during the entire programming

cycle for the addressed word.

- 4. Set the next input address and repeat steps 2 and 3 at a programming duty cycle of 35% maximum. This procedure is repeated for each input address for which a specific output word pattern is desired. A low logic level can always be changed to a high logic level simply by repeating Steps 1 and 2. Once programmed to provide a high logic level, the output cannot be changed to supply a low logic level.

- NOTE: When verification indicates that a bit did not program, repeat steps 2 through 4. If the bit did not program after the second application of a 1-millisecond programming pulse, repeat steps 2 through 4 using programming pulse time of 10 to 20 milliseconds. Regardless of the programming pulse duration, its total average pulse time should be no more than 35% of the programming culse.

FIGURE 1-PROGRAMMING CONNECTIONS

# TYPES SN54188A, SN74188A, AND SERIES 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

#### recommended conditions for programming

|                                                           |                    |      | '188A                |             | SNS  | 54S', SN              | 74S' |    |

|-----------------------------------------------------------|--------------------|------|----------------------|-------------|------|-----------------------|------|----|

|                                                           |                    | MIN  | NOM                  | MAX         | MIN  | NOM                   | MAX  |    |

| Supply voltage, V <sub>CC</sub> (see Note 6)              | Steady state       | 4.75 | 5                    | 5,75        | 4.75 | 5                     | 5.75 | V  |

| Supply voltage, VCC (see Note of                          | Program pulse      | 10   | 10.5                 | 11†         | 10   | 10.5                  | 11†  | ſ  |

| Input voltage                                             | High level, VIH    | 2.4  |                      | 5           | 2.4  | _                     | 5    |    |

| input voltage                                             | Low level, VIL     | 0    |                      | 0.5         | 0    |                       | 0.5  | Ĩ  |

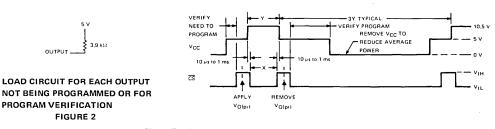

| Termination of all outputs except the one to be           | programmed         |      | load cir<br>Figure 2 |             |      | load cire<br>Figure 2 |      |    |

| Voltage applied to output to be programmed, V             | D(pr) (see Note 7) |      | 0.25                 | +0.3<br>0.8 | 0    | 0.25                  | 0.3  | v  |

| Duration of V <sub>CC</sub> programming pulse Y (see Figu | re 3 and Note 8)   | 1    |                      | 20          | 1    |                       | 20   | ms |

| Programming duty cycle                                    |                    |      | 25                   | 35          |      | 25                    | 35   | %  |

| Free-air temperature                                      |                    | 0    |                      | 55          | 0    |                       | 55   | °c |

<sup>†</sup>Absolute maximum ratings.

NOTES: 6. Voltage values are with respect to the GND 2 terminals.

The '188A, 'S188, 'S288, 'S470, 'S471, 'S472, and 'S473 are supplied with all bit locations containing a low logic level, and programming a bit changes the output of the bit to high logic level. The 'S287 and 'S387 are supplied with all bit outputs at a high logic level, and programming a bit changes it to a low logic level.

8. Programming is guaranteed if the pulse applied is 10 ms long. Typically, programming occurs in 1 ms.

#### step-by-step programming procedure

- 1. Apply steady-state supply voltage ( $V_{CC}$  = 5 V) and address the word to be programmed.

- 2. Verify that the bit location needs to be programmed. If not, proceed to the next bit.

- If the bit requires programming, disable the outputs by applying a high-logic-level voltage to the chip-select input(s).

- 4. Only one bit location is programmed at a time. Connect each output not being programmed to 5 V through 3.9 kΩ and apply the voltage specified in the table to the output to be programmed. Maximum current out of the programming output supply during programming is 150 mA.

- 5. Step V<sub>CC</sub> to 10.5 V nominal. Maximum supply current required during programming is 750 mA.

- Apply a low-logic-level voltage to the chip-select input(s). This should occur between 10 μs and 1 ms after V<sub>CC</sub> has reached its 10.5-V level. See programming sequence of Figure 3.

- 7. After the X pulse time (1 ms) is reached, a high logic level is applied to the chip-select inputs to disable the outputs.

- 8. Within 10  $\mu$ s to 1 ms after the chip-select input(s) reach a high logic level, V<sub>CC</sub> should be stepped down to 5 V at which level verification can be accomplished.

- The chip-select input(s) may be taken to a low logic level (to permit program verification) 10 μs or more after V<sub>CC</sub> reaches its steady-state value of 5 V.

- 10. At a Y pulse duty cycle of 35% or less, repeat steps 1 through 8 for each output where it is desired to program a bit.

- NOTES: A) V<sub>CC</sub> should be removed between program pulses to reduce dissipation and chip temperatures. See Figure 3.

B) When verification indicates that a bit did not program, repeat steps 3 through 9. If the bit did not program after the second application of a 1-ms X pulse, repeat steps 3 through 9 using an X pulse time of 10 to 20 ms. Regardless of the X duration, the total average pulse time of Y should be no more than 35% of the programming cycle.

# **TYPES SN54186, SN54188A, SN74186, SN74188A PROGRAMMABLE READ-ONLY MEMORIES**

### recommended operating conditions

|                                    |     | SN54186  |     |      | SN74186 |      |      |

|------------------------------------|-----|----------|-----|------|---------|------|------|

|                                    | S   | SN54188A |     |      | N74188  | A    | UNIT |

|                                    | MIN | NOM      | MAX | MIN  | NOM     | MAX  |      |

| Supply voltage, V <sub>CC</sub>    | 4.5 | 5        | 5,5 | 4.75 | 5       | 5.25 | v    |

| High-level output voltage, VOH     |     |          | 5.5 |      |         | 5.5  | V    |

| Low-level output current, IOL      |     |          | 12  |      |         | 12   | mA   |

| Operating free-air temperature, TA | -55 |          | 125 | 0    |         | 70   | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|       | PARAMETER                                 | -                                                  | EST CONDITI             | owst                    |     | <b>'18</b> 6 |      |     | '188A |      |      |

|-------|-------------------------------------------|----------------------------------------------------|-------------------------|-------------------------|-----|--------------|------|-----|-------|------|------|

|       | FARAMETER                                 |                                                    | ESTCONDITI              | UNS.                    | MIN | TYP‡         | MAX  | MIN | TYP‡  | MAX  | UNIT |

| VIH   | High-level input voltage                  |                                                    |                         |                         | 2   |              |      | 2   |       |      | V    |

| VIL   | Low-level input voltage                   |                                                    |                         |                         |     |              | 0.8  |     |       | 0.8  | V    |

| VIK   | Input clamp voltage                       | V <sub>CC</sub> = MIN,                             | I <sub>I</sub> = -12 mA |                         |     |              | -1.5 |     |       | -1.5 | V    |

| 1     | High lough output ourgant                 | V <sub>CC</sub> = MIN,                             | V <sub>IH</sub> = 2 V,  | V <sub>OH</sub> = 2.4 V |     |              | 100  |     |       |      |      |

| юн    | High-level output current                 | V <sub>IL</sub> = 0.8 V                            |                         | V <sub>OH</sub> = 5.5 V |     |              | 200  |     |       | 100  | μA   |

| VOL   | Low-level output voltage                  | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, |                         |                         |     |              | 0.4  |     |       | 0.45 | v    |

| II.   | Input current at maximum<br>input voltage | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V  |                         |     |              | 1    |     |       | 1    | mA   |

| Чн    | High-level input current                  | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.4 V  |                         |     |              | 40   |     |       | 40   | μA   |

| ΊL    | Low-level input current                   | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0.4 V  |                         |     |              | -1   |     |       | -1   | mA   |

| 1.0.0 | Supply current                            |                                                    | See Nets 0              | Both CS at 0 V          |     | 47           | 95   |     |       |      |      |

| ICC   | Supply current                            | V <sub>CC</sub> = MAX,                             | See Note 9              | Both CS at 4.5 V        |     | 80           | 120  |     |       |      | mA   |

| Іссн  | Supply current, all outputs high          | Vcc = MAX                                          |                         | See Note 10             |     |              |      |     | 50    | 80   |      |

| ICCL  | Supply current, all outputs low           |                                                    |                         | See Note 11             |     |              |      |     | 82    | 110  | mA   |

| Co    | Off-state output capacitance              | V <sub>CC</sub> = 5 V,                             | V <sub>0</sub> = 2 V,   | f = 1 MHz               |     | 6.5          |      |     | 6.5   |      | рF   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. <sup>‡</sup>All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

NOTES: 9. ICC of '186 is measured with all outputs open and the address inputs at 4.5 V. Typical values are for 50% of the bits programmed.

I<sub>CCH</sub> of '188A is measured with all inputs at 4.5 V, all outputs open.

I<sub>CCL</sub> of '188A is measured with the chip-select input grounded, all other inputs at 4.5 V, and all outputs open. The typical value shown is for the worst-case condition of all eight outputs low at one time. This condition may not be possible after the device has been programmed.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$

| түре  | TEST CONDITIONS                             | t <sub>a(ad)</sub> (ns)<br>Access time from<br>address |     | Access ti | t <sub>a</sub> (CS/ <del>CS</del> ) (ns)<br>Access time from<br>chip select (enable time) |     | y (ns)<br>1 delay time,<br>-level output<br>5t (disable time) |

|-------|---------------------------------------------|--------------------------------------------------------|-----|-----------|-------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------|

|       |                                             | TYP                                                    | MAX | ТҮР       | MAX                                                                                       | TYP | MAX                                                           |

| '186  | $C_{L} = 30  pF$ , $R_{L1} = 400  \Omega$ , | 50                                                     | 75  | 55        | 75                                                                                        | 40  | 75                                                            |

| '188A | $R_{L2} = 600 \Omega$ , See Figure 4        | 30                                                     | 50  | 34        | 50                                                                                        | 23  | 50                                                            |

# **SERIES 54S/74S PROGRAMMABLE READ-ONLY MEMORIES WITH OPEN-COLLECTOR OUTPUTS**

#### recommended operating conditions

|                                              |            |      | ′S188 |      | 's   | UNIT |      |     |

|----------------------------------------------|------------|------|-------|------|------|------|------|-----|

|                                              |            | MIN  | NOM   | MAX  | MIN  | NOM  | MAX  | 1   |

|                                              | Series 54S | 4.5  | 5     | 5.5  | 4.5  | 5    | 5.5  | v   |

| Supply voltage, V <sub>CC</sub>              | Series 74S | 4.75 | 5     | 5.25 | 4.75 | 5    | 5.25 | 1 ° |

| High-level output voltage, VOH               |            |      |       | 5.5  |      |      | 5.5  | V   |

| Low-level output current, IOL                |            |      |       | 20   |      |      | 16   | mA  |

| Operating free-air temperature, $T_{\Delta}$ | Series 54S | -55  |       | 125  | -55  |      | 125  | °c  |

| Operating nee-an temperature, 1 A            | Series 74S | 0    |       | 70   | 0    |      | 70   |     |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| [     | PARAMETER                              | TEST CONDITIO                                      | ONS <sup>†</sup> | MIN | TYP‡ | MAX  | UNIT          |

|-------|----------------------------------------|----------------------------------------------------|------------------|-----|------|------|---------------|

| ⊻ін   | High-level input voltage               |                                                    |                  | 2   |      |      | V             |

| VIL   | Low-level input voltage                |                                                    |                  |     |      | 0.8  | V             |

| VIK   | Input clamp voltage                    | V <sub>CC</sub> = MIN, I                           | =18 mA           |     |      | -1.2 | V             |

|       | High-level output current              | V <sub>CC</sub> = MIN, V<br>V <sub>IH</sub> = 2 V, | OH = 2.4 V       |     |      | 50   | μA            |

| I OH. |                                        |                                                    | OH = 5.5 V       |     |      | 100  | <sup>#A</sup> |

| VOL   | Low-level output voltage               |                                                    | IH = 2 V,        |     |      | 0.5  | v             |

|       |                                        |                                                    | DL = MAX         |     |      |      |               |

| 4     | Input current at maximum input voltage | V <sub>CC</sub> = MAX, V                           | = 5.5 V          |     |      | 1    | mA            |

| Гн    | High-level input current               | V <sub>CC</sub> = MAX, V                           | = 2.7 V          |     |      | 25   | μA            |

| կլ    | Low-level input current                | V <sub>CC</sub> = MAX, V                           | i = 0.5 V        |     |      | -250 | μA            |

|       |                                        | V <sub>CC</sub> = MAX,                             | ′S188            |     | 80   | 110  |               |

| Ι.    | Country of the second                  | Chip select(s) at 0 V,                             | ʻ\$387           |     | 100  | 135  | 1.1           |

| l lcc | Supply current                         | Outputs open,                                      | 'S470            |     | 110  | 155  | mA            |

|       |                                        | See Note 12                                        | 'S473            |     | 120  |      |               |

### switching characteristics over recommended ranges of TA and VCC (unless otherwise noted)

| ТҮРЕ     | TEST CONDITIONS          | Access tir | t <sub>a(ad)</sub> (ns)<br>Access time from<br>address |      | (ns)<br>ne from<br>nable time) | tpLH (ns)<br>Propagation delay time,<br>low-to-high-level output<br>from chip select (disable time) |     |

|----------|--------------------------|------------|--------------------------------------------------------|------|--------------------------------|-----------------------------------------------------------------------------------------------------|-----|

|          |                          | TYP‡       | MAX                                                    | TYP‡ | MAX                            | TYP‡                                                                                                | MAX |

| SN54S188 |                          | 25         | 50                                                     | 12   | 30                             | 12                                                                                                  | 30  |

| SN74S188 |                          | 25         | 40                                                     | 12   | 25                             | 12                                                                                                  | 25  |

| SN54S387 | C <sub>L</sub> = 30 pF,  | 42         | 75                                                     | 15   | 40∮                            | 15                                                                                                  | 40∮ |

| SN74S387 | R <sub>L1</sub> = 300 Ω, | 42         | 65                                                     | 15   | 35                             | 15                                                                                                  | 35  |

| SN54S470 | R <sub>L2</sub> = 600 Ω, | 50         | 80                                                     | 20   | 40                             | 15                                                                                                  | 35  |

| SN74S470 | See Figure 4             | 50         | 70                                                     | 20   | 35                             | 15                                                                                                  | 30  |

| SN54S473 |                          | 55         |                                                        | 20   |                                | 15                                                                                                  |     |

| SN74S473 |                          | 55         |                                                        | 20   |                                | 15                                                                                                  |     |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup>All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

An SN54S387 in the W package operating at free-air temperatures above 108°C requires a heat sink that provides a thermal resistance from case to free air,  $R_{\theta CA}$ , of not more than 42 °C/W.

∮Tentative specifications.

NOTE 12: The typical values of I<sub>CC</sub> shown are with all outputs low.

# SERIES 54S/74S **PROGRAMMABLE READ-ONLY MEMORIES WITH 3-STATE OUTPUTS**

#### recommended operating conditions

|                                              |            | 's   | ′S287<br>471, ′S4 | 72   |      | 'S288 |      | UNIT |

|----------------------------------------------|------------|------|-------------------|------|------|-------|------|------|

|                                              |            | MIN  | NOM               | MAX  | MIN  | NOM   | MAX  | 1    |

| Supply voltage Mag                           | Series 54S | 4.5  | 5                 | 5.5  | 4.5  | 5     | 5.5  | v    |

| Supply voltage, VCC                          | Series 74S | 4.75 | 5                 | 5.25 | 4.75 | 5     | 5.25 | 1 °  |

|                                              | Series 54S |      |                   | 2    |      |       | -2   |      |

| High-level output current, IOH               | Series 74S |      |                   | -6.5 |      |       | -6.5 | mA   |

| Low-level output current, IOL                |            |      |                   | 16   |      |       | 20   | mA   |

| Operating free-air temperature, $T_{\Delta}$ | Series 54S | -55  |                   | 125  | -55  |       | 125  | °c   |

| operating nee-an temperature, 1A             | Series 74S | 0    |                   | 70   | 0    |       | 70   |      |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | BABAMETER                                               | TEST CONDITIONS <sup>†</sup>                                      |                                                 | SN54S' |                  |                   | SN74S' |                  |                   |      |

|-----------------|---------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|--------|------------------|-------------------|--------|------------------|-------------------|------|

| PARAMETER       |                                                         | TEST CONDITIONS'                                                  |                                                 | MIN    | TYP‡             | MAX               | MIN    | түр‡             | MAX               | UNIT |

| VIH             | High-level input voltage                                |                                                                   |                                                 | 2      |                  |                   | 2      |                  |                   | V    |

| VIL             | Low-level input voltage                                 |                                                                   |                                                 |        |                  | 0.8               | -      |                  | 0,8               | V    |

| VIK             | Input clamp voltage                                     | V <sub>CC</sub> = MIN,                                            | l <sub>l</sub> = –18 mA                         |        |                  | -1.2              |        |                  | -1.2              | V    |

| v <sub>он</sub> | High-level output voltage                               | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V,                | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = MAX | 2.4    | 3.4              |                   | 2.4    | 3.2              |                   | v    |

| VOL             | Low-level output voltage                                | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V,                | V <sub>1H</sub> = 2 V,<br>I <sub>OL</sub> = MAX |        |                  | 0.5               |        |                  | 0.5               | v    |

| IOZH            | Off-state output current,<br>high-level voltage applied | V <sub>CC</sub> = MAX,<br>V <sub>O</sub> = 2.4 V                  | V <sub>IH</sub> = 2 V,                          |        |                  | 50                |        |                  | 50                | μA   |

| 'ozl            | Off-state output current,<br>low-level voltage applied  | V <sub>CC</sub> = MAX,<br>V <sub>O</sub> = 0.5 V                  | V <sub>IH</sub> = 2 V,                          |        |                  | -50               |        |                  | -50               | μA   |

| II.             | Input current at maximum<br>input voltage               | V <sub>CC</sub> = MAX,                                            | V <sub>I</sub> = 5.5 V                          |        |                  | 1                 |        |                  | 1                 | mA   |

| Чн              | High-level input current                                | V <sub>CC</sub> = MAX,                                            | V <sub>I</sub> = 2.7 V                          |        |                  | 25                |        |                  | 25                | μA   |

| hL              | Low-level input current                                 | V <sub>CC</sub> = MAX,                                            | V <sub>I</sub> = 0.5 V                          |        |                  | -250              |        |                  | -250              | μA   |

| los             | Short-circuit output current§                           | V <sub>CC</sub> = MAX                                             |                                                 | -30    |                  | -100              | -30    |                  | -100              | mA   |

| lcc             | Supply current                                          | V <sub>CC</sub> = MAX,<br>Chip select(s) at 0 V,<br>Outputs open, | 'S287<br>'S288<br>'S471                         |        | 100<br>80<br>110 | 135<br>110<br>155 |        | 100<br>80<br>110 | 135<br>110<br>155 | mA   |

|                 |                                                         | See Note 12                                                       | 'S472                                           |        | 120              |                   |        | 120              |                   | 1    |

### switching characteristics over recommended ranges of TA and VCC (unless otherwise noted)

| ТҮРЕ     | TEST CONDITIONS                                                                                                                                                  | t <sub>a(ad)</sub> (ns)<br>Access time<br>from address |     | t <sub>a</sub> ( <del>CS</del> ) (ns)<br>Access time from<br>chip select (enable time) |     | tpxz (ns)<br>Disable time from<br>high or low level |     |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|----------------------------------------------------------------------------------------|-----|-----------------------------------------------------|-----|

|          |                                                                                                                                                                  | TYP‡                                                   | MAX | түр‡                                                                                   | MAX | TYP‡                                                | MAX |

| SN54S287 | C <sub>L</sub> = 30 pF for<br>t <sub>a(ad)</sub> and t <sub>a</sub> ( <del>C</del> S),<br>5 pF for tpχ <sub>Z</sub> ;<br>R <sub>L</sub> = 300 Ω;<br>See Figure 5 | 42                                                     | 75∮ | 15                                                                                     | 40∮ | 12                                                  |     |

| SN74S287 |                                                                                                                                                                  | 42                                                     | 65  | 15                                                                                     | 35  | 12                                                  |     |

| SN54S288 |                                                                                                                                                                  | 25                                                     | 50  | 12                                                                                     | 30  | 8                                                   | .30 |

| SN74S288 |                                                                                                                                                                  | 25                                                     | 40  | 12                                                                                     | 25  | 8                                                   | 20  |

| SN54S471 |                                                                                                                                                                  | 50                                                     | 80  | 20                                                                                     | 40  | 15                                                  | 35  |

| SN74S471 |                                                                                                                                                                  | 50                                                     | 70  | 20                                                                                     | 35  | 15                                                  | 30  |

| SN54S472 |                                                                                                                                                                  | 55                                                     |     | 20                                                                                     |     | 15                                                  |     |

| SN74S472 |                                                                                                                                                                  | 55                                                     |     | 20                                                                                     |     | 15                                                  |     |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

An SN54S287 in the W package operating at free-air temperatures above 108°C requires a heat sink that provides a thermal resistance from case-to-free-air, R<sub>0CA</sub>, of not more than 42°C/W.

NOTE 12: The typical values of I<sub>CC</sub> shown are with all outputs low.

575

# SERIES 54/74, 54S/74S PROGRAMMABLE READ-ONLY MEMORIES

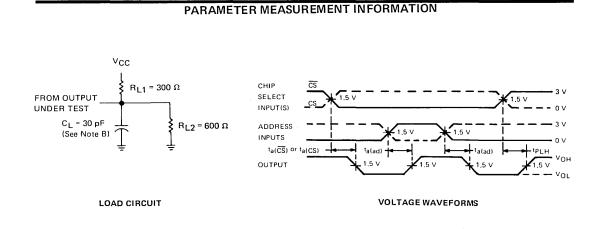

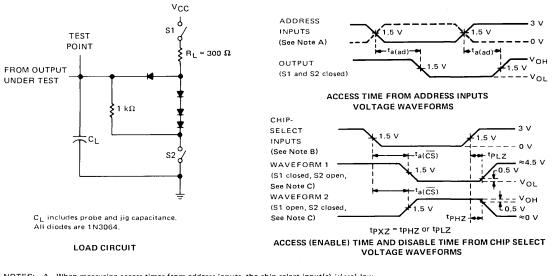

- NOTES: A. The input pulse generator has the following characteristics:  $Z_{out} \approx 50 \ \Omega$  and PRR  $\leq$  1 MHz. For Series 54/74, tr  $\leq$  7 ns,  $t_f \leqslant 7$  ns. For Series 54S/74S,  $t_r \leqslant 2.5$  ns,  $t_f \leqslant 2.5$  ns. B. CL includes probe and jig capacitance.

- C. The pulse generator is connected to the input under test. The other inputs, memory content permitting, are connected so that the input will switch the output under test .

#### FIGURE 4-SWITCHING TIMES OF '186, '188A, 'S188, 'S470, 'S387, AND 'S473

NOTES: A. When measuring access times from address inputs, the chip-select input(s) is(are) low.

- B. When measuring access and disable times from chip-select input(s), the address inputs are steady-state.

- C. Waveform 1 is for the output with internal conditions such that the output is low except when disabled. Waveform 2 is for the output with internal conditions such that the output is high except when disabled.

- D. Input waveforms are supplied by pulse generators having the following characteristics:  $t_r \le 2.5$  ns,  $t_f \le 2.5$  ns, PRR  $\le 1$  MHz, and  $Z_{out} \approx 50 \ \Omega$ .

#### FIGURE 5-SWITCHING TIMES OF 'S287, 'S288, 'S471, AND 'S472

PRINTED IN U.S.A.

575

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

TEXAS INSTRUMENTS RESERVES THE RIGHT TO MAKE CHANGES AT ANY TIME IN ORDER TO IMPROVE DESIGN AND TO SUPPLY THE BEST PRODUCT POSSIBLE.

# TEXAS INSTRUMENTS

POST OFFICE BOX 5012 . DALLAS, TEXAS 75222