- Package Options Include Both Plastic and Ceramic Chip Carriers in Addition to Plastic and Ceramic DIPs

- Dependable Texas Instruments Quality and Reliability

## description

These devices contain four independent 2-input NOR gates. They perform the Boolean functions  $Y = \overline{A + B}$  or  $Y = \overline{A \cdot B}$  in positive logic.

The SN54HC36 is characterized for operation over the full military temperature range of -55°C to 125°C. The SN74HC36 is characterized for operation from -40°C to 85°C.

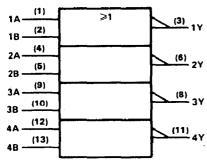

# logic symbol

Pin numbers shown are for J and N packages.

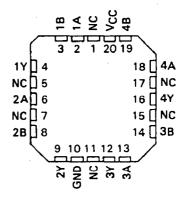

#### SN54HC36 . . . J PACKAGE SN74HC36 . . . J OR N PACKAGE (TOP VIEW)

| 1A 🗌  | 1 | U14  | □vcc |

|-------|---|------|------|

| 1B 🗌  | 2 | 13   | ☐ 4B |

| 1Y 🗌  | 3 | . 12 | ] 4A |

| 2A 🗌  | 4 | 11   | ☐ 4Y |

| 2B 🗌  | 5 | 10   | ] 3B |

| 2Y 🗌  | 6 | 9    | ] 3A |

| GND [ | 7 | 8    | ] 3Y |

SN54HC36 ... FH OR FK PACKAGE SN74HC36 ... FH OR FN PACKAGE (TOP VIEW)

NC-No internal connection

## FUNCTION TABLE (each gate)

| INPUTS |     | OUTPUT |  |  |

|--------|-----|--------|--|--|

| Α      | В   | Y      |  |  |

| Н      | Х   | L      |  |  |

| Х      | Н   | L      |  |  |

| L      | _ L | Н      |  |  |

maximum ratings, recommended operating conditions, and electrical characteristics

See Table I, page 2-4.

# switching characteristics over recommended operating free-air temperature range (unless otherwise noted), $C_L = 50 \text{ pF}$ (see Note 1)

| PARAMETER       | FROM TO          |          | ,,    | T <sub>A</sub> = 25°C |     | SN54HC36 |     | SN74HC36 |     | UNIT |       |

|-----------------|------------------|----------|-------|-----------------------|-----|----------|-----|----------|-----|------|-------|

| PARAMETER       | (INPUT) (OUTPUT) | (OUTPUT) | vcc   | MIN                   | TYP | MAX      | MIN | MAX      | MIN | MAX  | CIVIT |

|                 | A or B           |          | 2 V   |                       | 50  | 100      |     | 150      |     | 125  |       |

| <sup>t</sup> pd |                  | Y        | 4.5 V | i                     | 10  | 20       |     | . 30     |     | 25   | ns    |

| •               |                  |          | 6 V   |                       | 8   | 17       |     | 25       |     | 21   |       |

|                 |                  |          | 2 V   |                       | 38  | 75       |     | 110      |     | 95   |       |

| tţ              | ļ                | Y        | 4.5 V |                       | 8   | 15       |     | 22       |     | 19   | ns    |

| -               | ŀ                | 1        | 6 V   | ļ                     | 6   | 13       |     | 19       |     | 16   | J     |

| C <sub>pd</sub> | Power dissipation capacitance per gate | No load, T <sub>A</sub> = 25°C | 20 pF typ |

|-----------------|----------------------------------------|--------------------------------|-----------|

|                 | <u> </u>                               |                                |           |

NOTE 1: For load circuit and voltage waveforms, see page 1-14.